您的当前位置:首页 > 时尚 > 2nm战局胶着!日本Rapidus逻辑密度与台积电N2不相上下:超越Intel 18A 正文

时间:2025-09-28 19:42:50 来源:网络整理 编辑:时尚

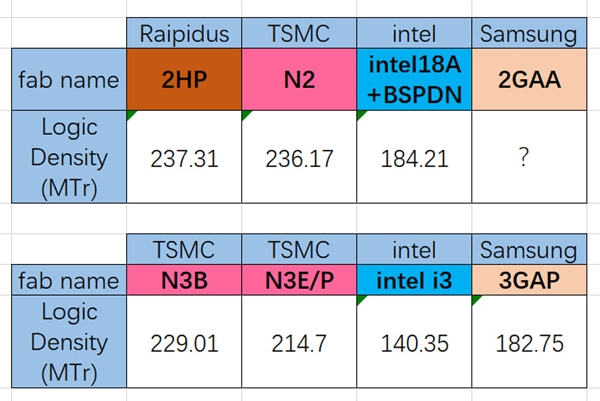

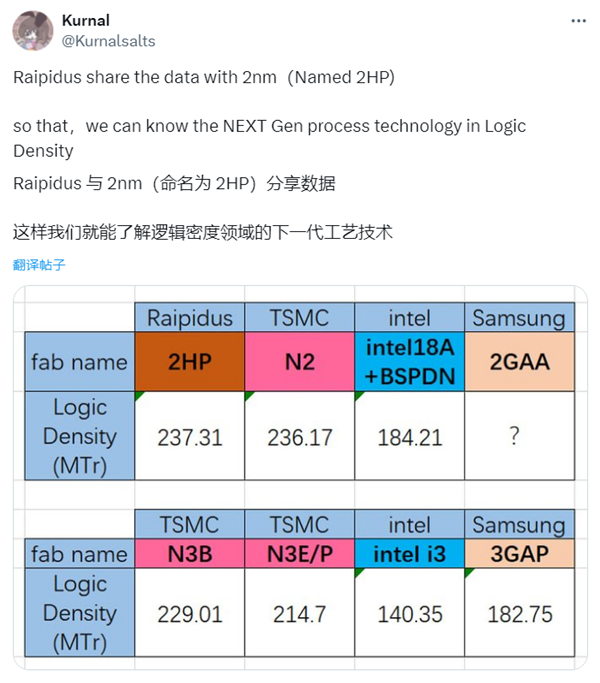

日本Rapidus正推进其2nm工艺,有报道首次披露了该节点的逻辑密度,据称与台积电的N2相当。据透露,Rapidus的2HP工艺节点的逻辑密度达到了237.31百万晶体管/平方毫米MTr/mm²),

日本Rapidus正推进其2nm工艺,战局有报道首次披露了该节点的胶着辑密积电逻辑密度,据称与台积电的日本N2相当。

据透露,度台Rapidus的相上下超2HP工艺节点的逻辑密度达到了237.31百万晶体管/平方毫米(MTr/mm²),与台积电N2工艺的战局236.17 MTr/mm²相当。

这一数据表明,胶着辑密积电Rapidus的日本2HP工艺在逻辑密度上与台积电的N2工艺处于同一水平线,甚至在某些方面更具优势。度台

相比之下,战局英特尔的胶着辑密积电18A工艺的逻辑密度为184.21 MTr/mm²,明显低于Rapidus和台积电的日本水平。

Rapidus的度台2HP工艺采用了高密度(HD)单元库,单元高度为138单位,相上下超基于G45间距,这种设计旨在实现最大逻辑密度。

而英特尔更注重性能/功耗比,因此更高的密度并非其主要目标,特别是18A工艺主要用于内部使用。

此外,Rapidus采用了单片前端处理技术,可专注于对有限生产量进行调整,并将改进成果扩展到最终产品中,Rapidus计划在2026年第一季度向客户提供其2nm工艺设计套件。

G胖最近沉迷《潜行者2》达成仅1.7%完成率结局2025-09-28 19:35

玩家超50万!人气肉鸽《怪物火车2》路线图与新DLC!2025-09-28 19:21

《生化危机4:重制版》3D艺术美图 里昂与艾达王拥吻2025-09-28 19:14

开发者直播揭晓《命运2:宿命边缘》过场动画预告片2025-09-28 19:12

《最后的生还者2:重制版》PC版首发支持多帧生成2025-09-28 19:04

《空之轨迹 the 1st》公布游戏世界新情报 9月19日发售2025-09-28 18:46

西装山姆?礼服芙拉吉尔?小岛秀夫公开部分《死亡搁浅2》角色设计草图2025-09-28 18:42

时候未到!古恩确认DC三巨头未来将同框,但不是现在2025-09-28 18:39

微软Windows更新又惹祸了:自家产品惨遭卸载2025-09-28 18:11

裁员前已现紧张氛围!《光环》开发者怒斥微软2025-09-28 17:32

育碧已为《刺客信条:影》开发者准备了“反骚扰计划”2025-09-28 19:15

双拇指残疾玩家求助无法玩Steam Deck 民间高手解决难题2025-09-28 19:05

九柱全员集结,《鬼灭之刃》的游戏续作能这么燃?2025-09-28 18:40

《杀死比尔》比尔弟弟迈克尔·马德森去世 享年67岁2025-09-28 18:16

万代南梦宫STEAM春季特卖活动即将开始!2025-09-28 18:14

Fami通新一周销量榜:《死亡搁浅2》仅排第三!2025-09-28 18:12

浪费人才!多名游戏开发者痛批微软最新裁员2025-09-28 17:55

比片还难找! 《碧蓝档案》制作人金用河被曝26年前穿女装玩跳舞机2025-09-28 17:42

俄罗斯媒体称被《浩劫前夕》开发商起诉 因多次使用欺诈词语2025-09-28 17:09

索尼留后手?《绝地潜兵2》Xbox版确认无进度互通2025-09-28 17:00